でも邪魔になるので没ですね。

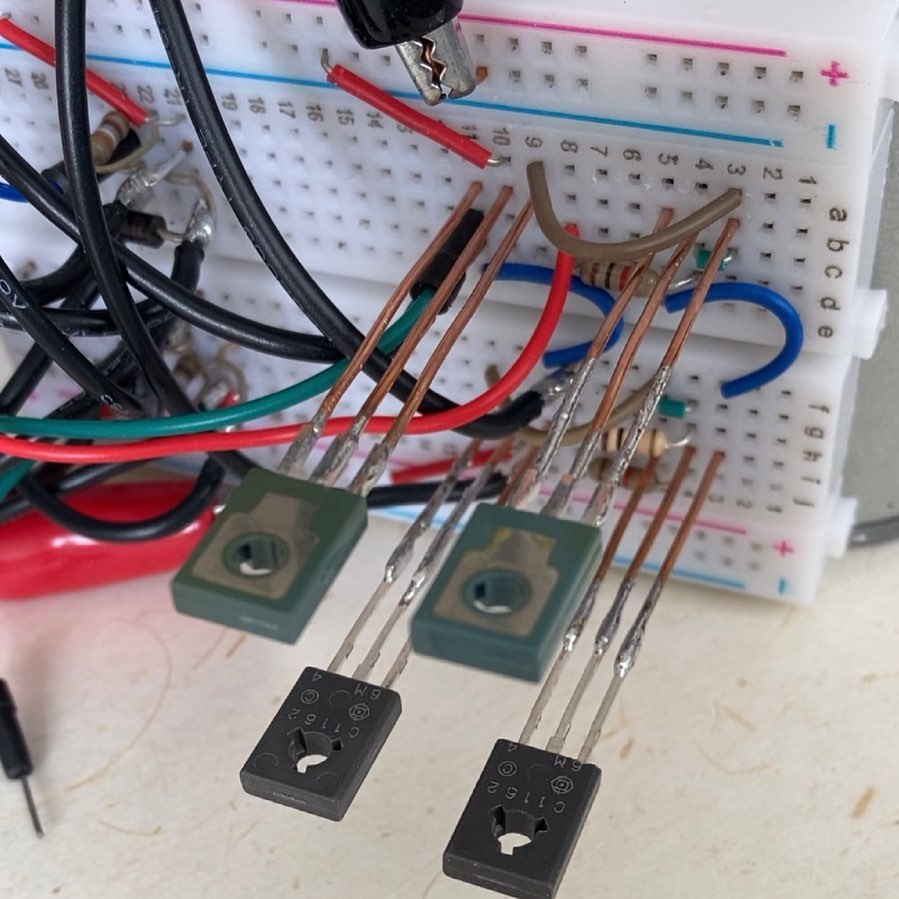

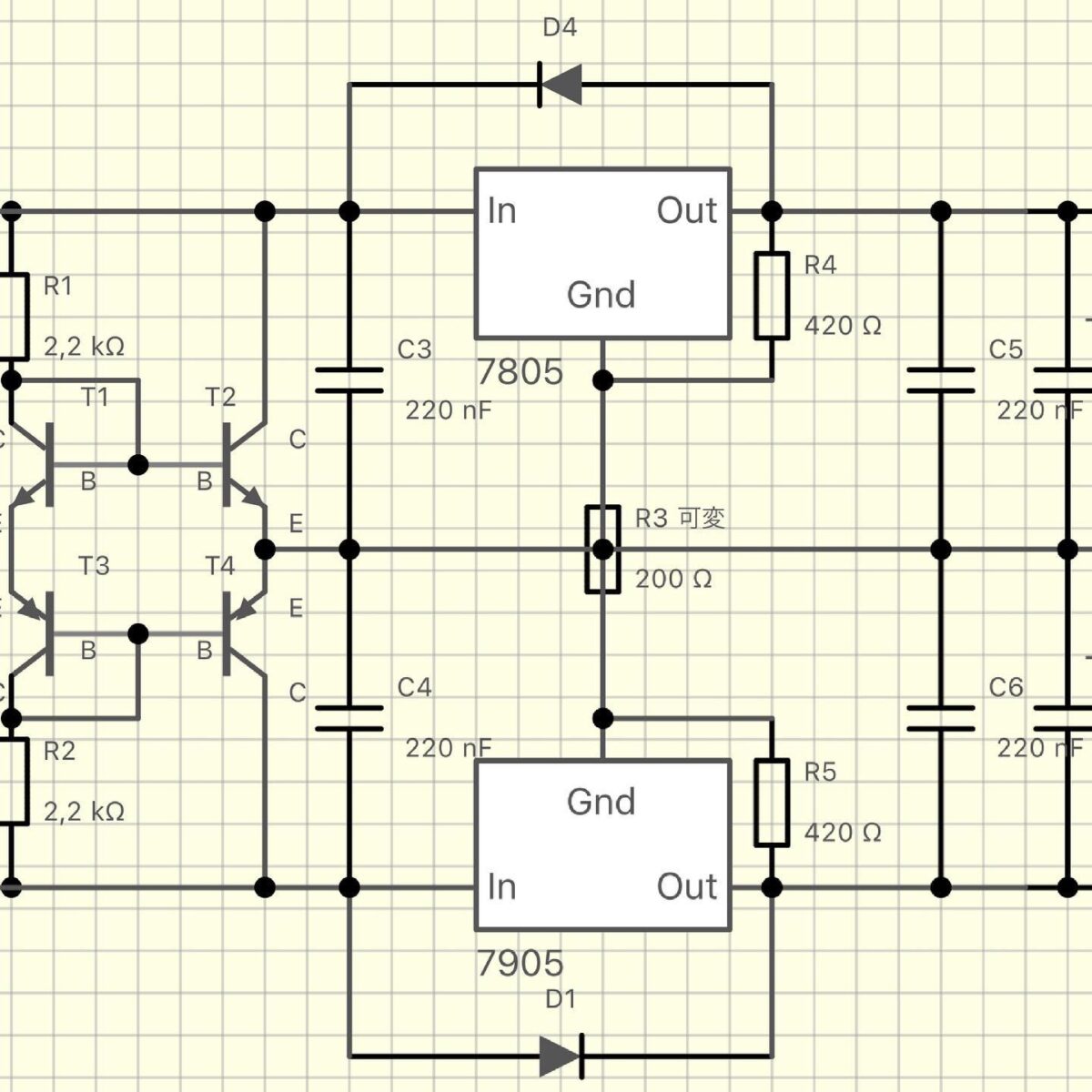

熱管理は難しいです。素人には手が出ません。

カテゴリに拘らず自由に投稿

に「演繹オブジェクト指向」云々とあります。システム名がキホーテというのですが、ちょっとネーミングが気になります。

プログラムから構造に関する部分を取り除く手法のようです。実際必要な機能とアプリケーションとしてまとめるための構造の部分が分離されていればなんと素晴らしいことでしょう。

期待が膨らみます。

https://www.jstage.jst.go.jp/article/jjsai/10/5/10_761/_article/-char/ja

動的継承演繹機構(Dynamic IDM : Inheritance Deduction Mecha-nism)

クラス間の継承関係を,演繹の結果に基づいて動的に変化させることができる

オブジェクトはメッセージを受け取り対応するメソッドを実行する。

メッセージに対応するメソッドがない場合はスーパークラスに対応するメソッドがないか探す。

スーパークラスに対応するメソッドがない場合はさらに遡ってスーパークラスに対応するメソッドがないか探す。これをルートクラスまで繰り返す。

ルートクラスまで遡っても見つからない場合は演繹システムにオブジェクトを送って対応するメソッドを探す。

メソッドが見つかった時点でそのメソッドが実行されるが見つからない時は例外処理を行う。

という流れで処理が進んでいくようです。メッセージを受け取ってその内容で処理を行うソフトウェアの仕組みはよくあります。

スーパークラスを遡ってもメッセージを処理する仕組みもよくあります。

アプリ内にメッセージに対応したメソッドがない場合は演繹システムにお願いする仕組みが特徴的ですね。

https://www.ueda.info.waseda.ac.jp/AITEC_ICOT_ARCHIVES/ICOT/HomePage-J.html

ここにアーカイブがあったので探検してみます。

から引用

「第五世代コンピュータ・プロジェクトは、大規模並列記号処理の諸技術、知識 情報処理の諸基礎技術の研究開発を行ない、大規模並列知識情報処理のための 一貫した技術体系を確立、これに基づく第五世代コンピュータ・プロトタイプ・ システムを構築した。また、その上に実用レベルの複雑さと規模を持つ実験的 応用ソフトウェアを構築し、技術体系の機能の適切性と実装の効率性を実践的 に検証した (詳細は資料2を参照)。」

素晴らしい目標です。

プロジェクトが大きいせいか資料がたくさんあり、どこから手をつけていくか迷うところです。それでこの目標の大規模並列知識情報処理をどのように実現したのかを最初の探検目標としてみます。

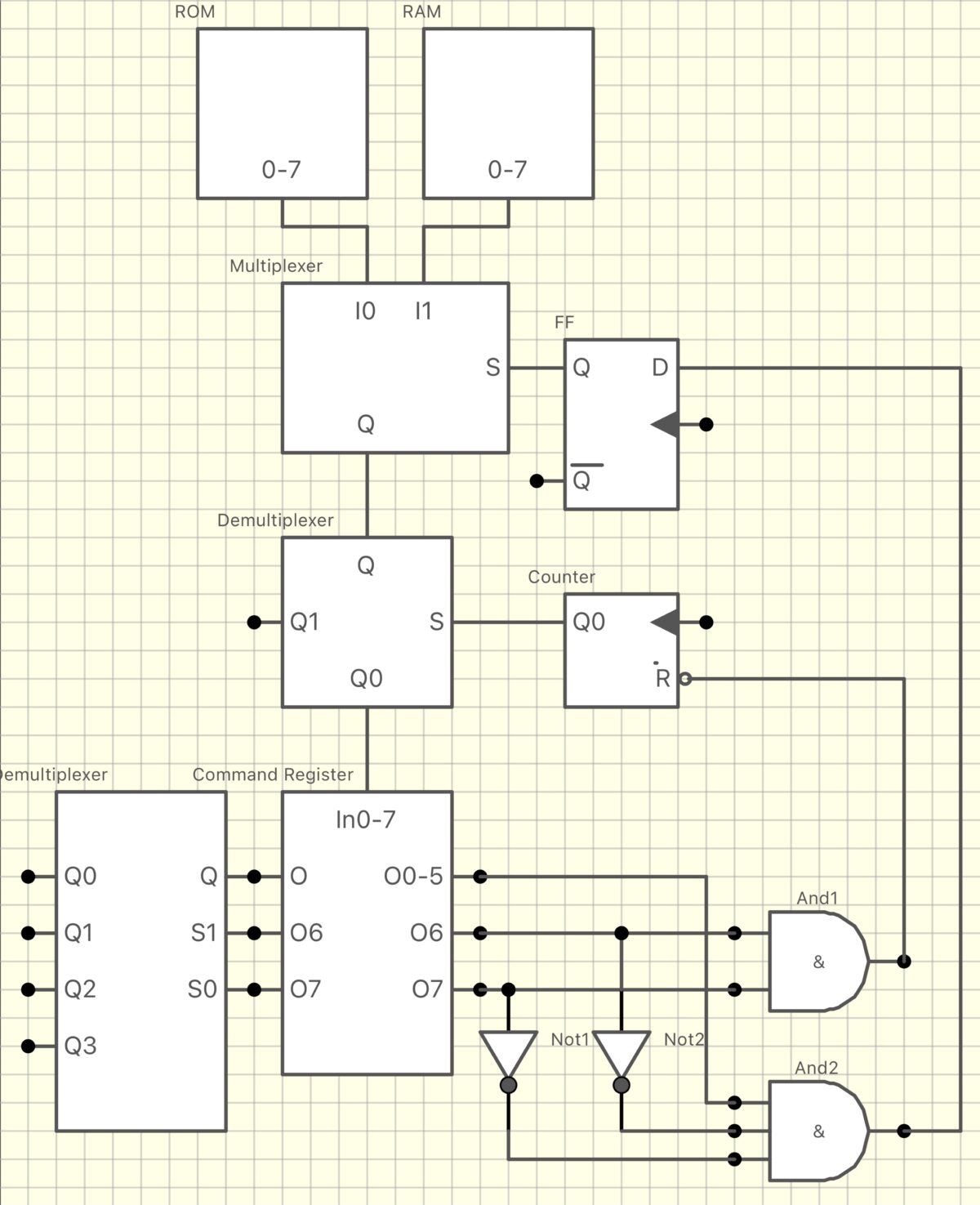

次に設計するのは最も難しい命令デコーダです。いきなり図が書けないので仕様を整理していきます。

リセット後、ROMの0000Hから実行される。

RAMにもプログラムを置けるので命令レジスタにロードする時に切り替えがある。

クロックごとにカウンターがアップされ次の命令が実行される。

命令長は8ビットまたは16ビットがあるのでメモリから読み出した後命令かデータか区別しなければならない。

なので

リセット

初期状態なので命令はROMからロードする

ROMの0000Hから命令レジスタにコマンドをロード

8ビット命令か16ビット命令か判定する

8ビット命令の時、次のクロックに移る

16ビット命令の時、次のクロックはデータとして処理し、その次は命令とする

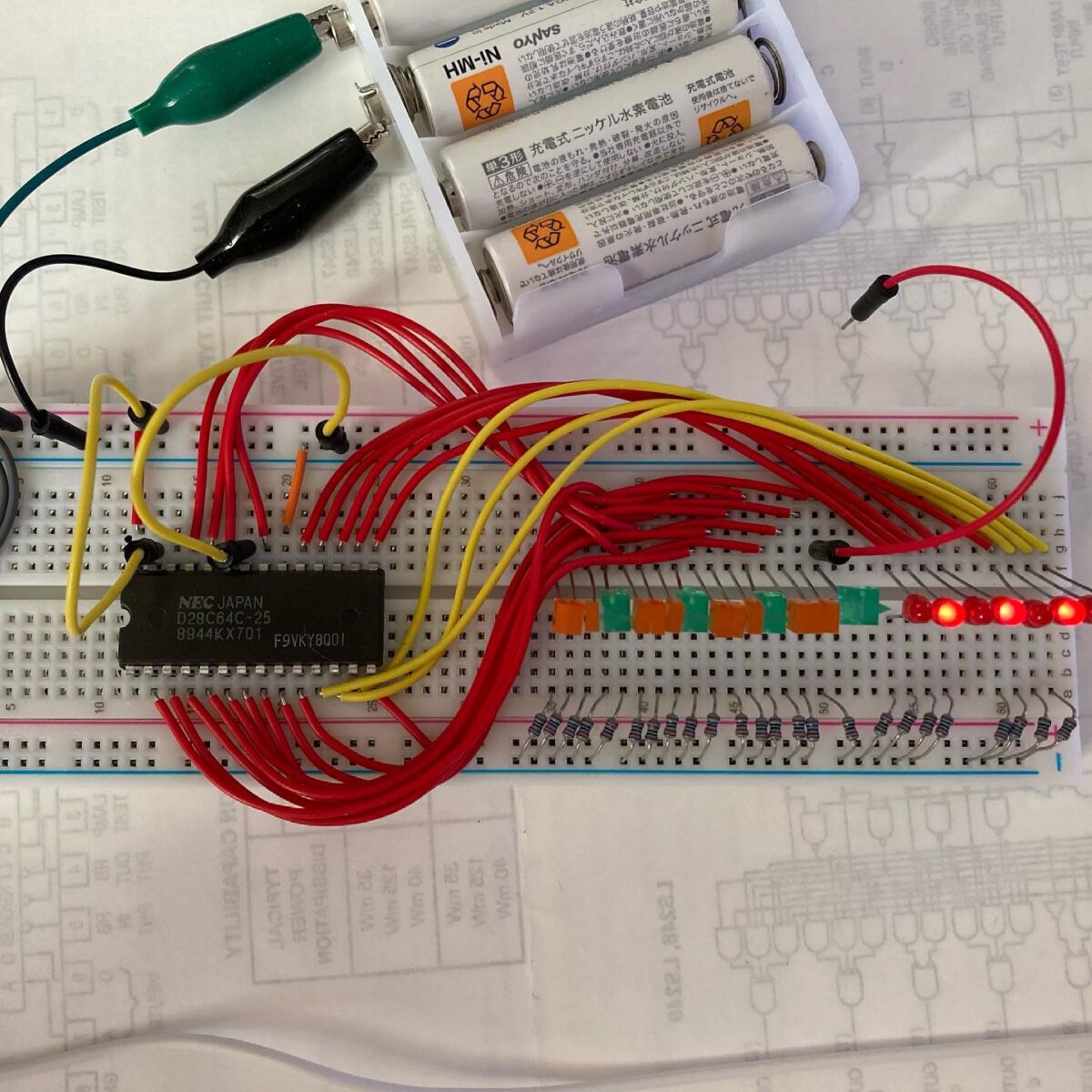

CPUを作るといっても個人のできる範囲でとなりますので再小規模で手作りします。現実的な方法としてロジックICで作ります。ネットで検索するとリレーやトランジスタで作っている人もいますが費用と手間を考えるととても真似できません。また、74LS181などのALUも使いません。命令の体系が一つのICに依存させると将来の制限に繋がるような気がするからです。

CPUの中枢がALUという人もいますが個性が発揮されるのはやはり命令デコーダになります。命令デコーダの設計によってそのシステムの個性が決まります。

部品数をなるべく減らしたいので出来る限り単純な命令デコーダを設計しようと思います。74LS154は4to16なのでこの範囲に収まるようにしていきます。

最近、益々人工知能と名打ったものやことが増えてきました。当然ながらそれを支えるテクノロジー分野でも人工知能を生みながら自らへの応用も盛んに行われているでしょう。

ならばソフトウェア開発も人工知能にお任せの時代がもうきているかもしれません。人類がソフトウェア開発から解放される日はいつなのでしょうか。

人工知能でソフトウェア開発できるようになったらCPUごとに異なるソフトウェアを開発しなくても良くなると思います。アーキテクチャが異なればそれに合わせてソフトウェアを作らなくても良く、きっと多様なCPUが普及していくでしょう。

そこで気が早いですが今から新しいCPUを作ってみます。人工知能でソフトウェア開発ができるようになる時代を見据えて新しい概念でできたら嬉しいです。

タイトルに付けた8n-Bit Computerとは最小構成が8bitなのですが利用環境に合わせて16bitでも32bitでも64bitでも128bitでもそれ以上でも使えるコンピュータです。途中で頓挫するかもしれませんがチャレンジしてみます。

前回の 0と1の列を8桁に揃えて16進数に置き換えてみました。そうするとマシン語と呼ばれているものになります。

出力:1000,0000 = 80

演算:0011,1000 = 38

入力:0111,1000 = 78

出力:1011,0000 = B0

演算:0000,1000 = 08

入力:0111,1000 = 78

桁は減りましたがまだただの数字なので覚え難いです。一目見てわかるような文字列に置き換えてみます。

80:OUTR

38:PASS

78:IN

B0:OUTA

08:AND

78:IN

命令のようになったので処理の流れが読めるようになってきました。

| OUTR | 出力をレジスタにする |

| PASS | 入力をそのまま出力する |

| IN | 入力を外部入力とする |

| OUTA | 出力をAとする |

| AND | AND演算する |

| IN | 入力を外部入力とする |

実際にROMに書き込むときはOUTRを逆に1000,0000に戻せば良いです。人間でもわかる単語で命令を順に記述し、それを2進数に置き換え、0は電圧をLowに、1は電圧をHighにしてROMに書き込みます。これこそがソフトウェアですね。

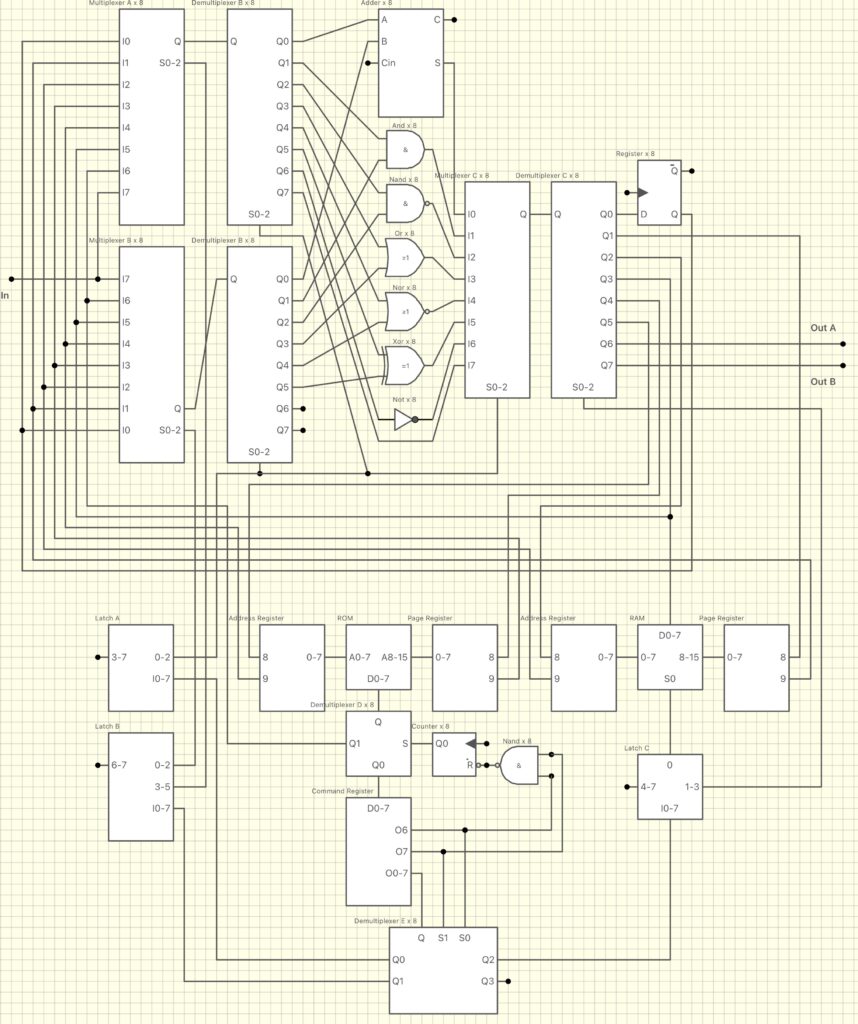

上図は最低限の機能を備えたコンピュータと思ってください。これでソフトウェアとは何かを考えてみます。

左側にあるInの状態をRegisterに写してみます。Inは8本のラインでそれぞれがHighかLowになります。

出力をRegisterにするためにはDemultiplexerCの出力がQ0になるようS0-2を000にします。

演算は必要ないのでDeMultiplexerA,BとMultiplexerCの出力をQ7にするためS0-2を111にします。

入力をInにするためにはMultiplexerAのI7がQに出てくるようにS 0-2を111にします。

これで出力先、演算方法、入力元を選択できました。

出力:000

演算:111

入力:111

となります。

出力、演算、入力に対する指示を切り替えているのはDemultiplexerEです。S0-1が

00:演算に対する命令

01:入力に対する命令

10:出力に対する命令

となります。

従って命令の切り替えると命令を合わせると、

出力:10,000

演算:00,111

入力:01,111

となります。

この要領でInとRegisterのAndをOutAに出力してみます。

出力:10,110

演算:00,001

入力:01,111,000

入力はAとBがあるので命令が長くなります。

このように 0と1の列をROMに書き込んでおいて順番に実行していけば様々な演算ができます。どのような列がどのように動作するかは上図の有り様によって決定されます。CPUが変わればそれにあった 0と1の列ではないと動作しないことがよくわかりました。

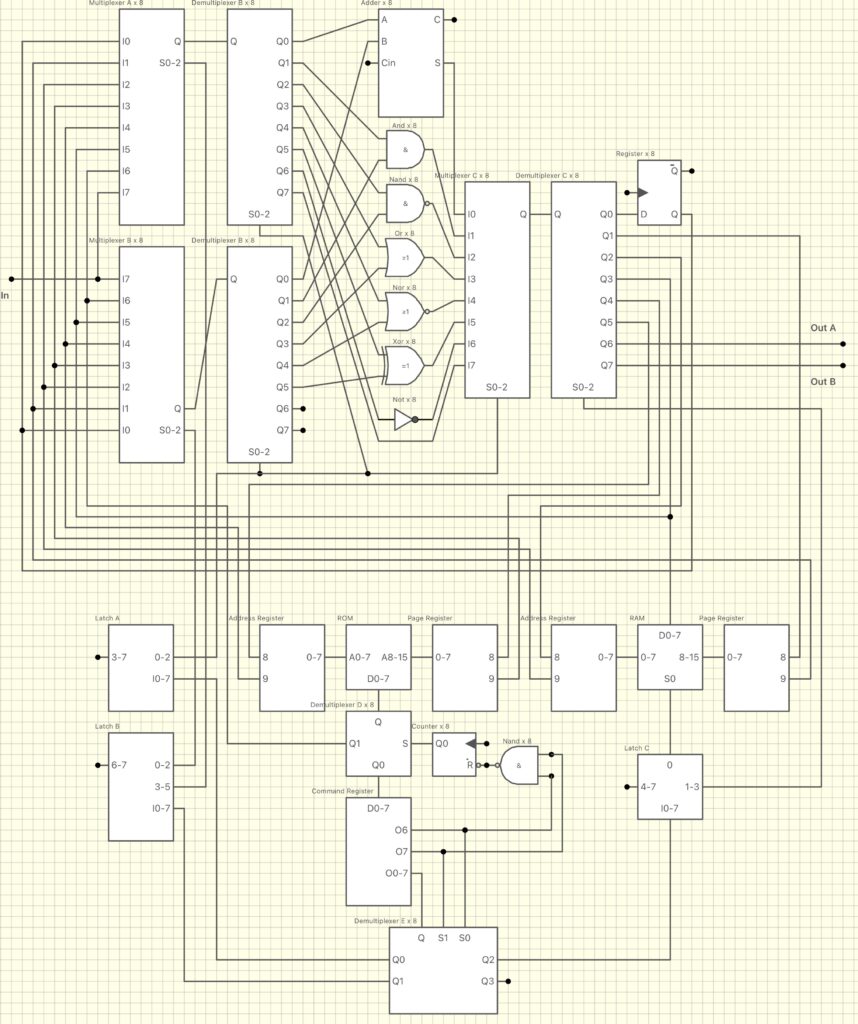

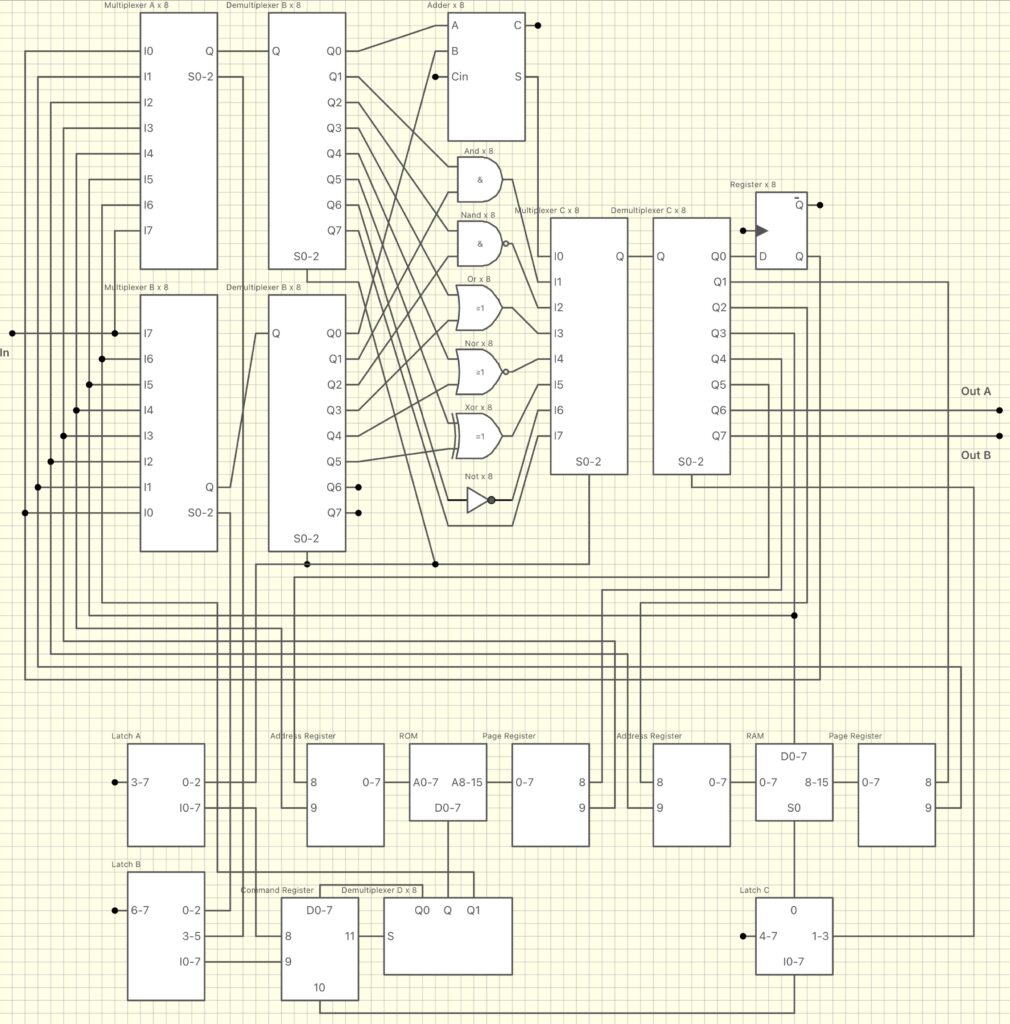

前回から更に拡張して、8ビットCPUを目指してみます。

入力

Register, RAM Address Register, RAM Page Register, RAM, ROM Address Register, ROM Page Register, ROM, In

出力

Register, RAM Address Register, RAM Page Register, RAM, ROM Address Register, ROM Page Register, Out A, Out B

演算

Adder, And, Or, Nand, Nor, Xor, Not, Pass

入力Aが8ライン、入力Bが8ライン、出力も8ライン、演算も8ラインの選択肢があります。

ROMから読み出された8ビットの命令がDeMultiplexerを通してCommand Registerに保存されます。この保存された命令のビット列に従い各MultiplexerやDeMultiplexerのライン切り替えが行われてプログラムされた演算を繰り返します。

だんだんCPUらしくなってきているようですが命令デコーダ部分が怪しげなのでもっと改良します。